时钟缓冲器NB3N2304NZDTG 高性能集成电路设计的关键驱动器

在高速数字系统和通信设备中,时钟信号的完整性、稳定性和低抖动是确保系统性能的基石。时钟缓冲器作为时钟树设计中的核心组件,其作用至关重要。美国安森美半导体(ON Semiconductor)推出的NB3N2304NZDTG便是一款专为高性能应用设计的LVCMOS/LVTTL时钟缓冲器/驱动器集成电路,它在现代集成电路设计中扮演着驱动与分配精准时钟的关键角色。

一、 器件概述与核心特性

NB3N2304NZDTG是一款1:4的差分至LVCMOS/LVTTL时钟缓冲器。其核心功能是接收一个差分或单端输入时钟信号,并将其转换为四路低电压、低抖动的CMOS/TTL电平输出。该器件设计用于满足高频、低相位噪声和低功耗的应用需求,典型工作频率可达200MHz以上。其主要特性包括:

- 低附加抖动:在优化时钟信号质量时,器件自身引入的抖动极低,这对于高速SerDes(串行器/解串器)、FPGA、网络处理器和测试测量设备的时序预算至关重要。

- 灵活的电源电压:支持3.3V或2.5V的VCC供电,输出可与1.8V、2.5V或3.3V的LVCMOS/LVTTL电平兼容,提供了出色的系统集成灵活性。

- 差分或单端输入:输入级设计既能接受LVPECL、LVDS或CML等差分信号,也能接收单端CMOS/TTL信号,通过内部偏置电路实现自动适配,简化了前端接口设计。

- 输出使能(OE)功能:集成的输出使能引脚允许用户将所有输出置于高阻态,便于电源管理和测试,有助于降低系统总功耗。

- 小型化封装:通常采用节省空间的TSSOP-16或类似封装,符合现代电子设备高密度PCB布局的要求。

二、 在集成电路与系统设计中的关键作用

在复杂的片上系统(SoC)或电路板设计中,NB3N2304NZDTG作为专用时钟驱动器,解决了以下几个关键设计挑战:

1. 时钟扇出与负载驱动

现代处理器、FPGA或ASIC通常需要将同一个参考时钟分配给多个负载。直接驱动可能导致时钟信号衰减、边沿速率下降和时序偏移。NB3N2304NZDTG提供了强大的输出驱动能力,能够驱动多达四个重负载,同时保持信号边沿陡峭,确保所有接收端时钟的一致性。

2. 信号电平转换与接口桥接

系统中常常存在不同电压域的器件。该缓冲器能够将来自时钟发生器(可能是LVPECL电平)的信号,干净、高效地转换为后端芯片所需的LVCMOS电平,充当了可靠的信号电平转换器和接口桥梁。

3. 改善信号完整性与减少抖动

时钟路径上的传输线效应、反射和串扰会劣化信号质量。NB3N2304NZDTG具有快速上升/下降时间和良好的输出对称性,能够重塑时钟波形,抑制振铃,并通过其低抖动特性有效净化时钟,为高速数据转换和传输提供纯净的时序参考。

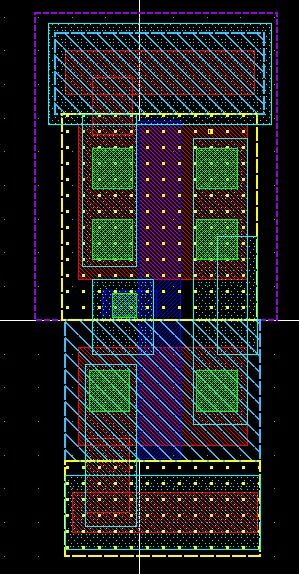

4. 时钟树综合与延时管理

虽然它本身不是可编程延时线,但其各输出通道间极低的输出到输出偏移(Skew)特性,对于构建平衡的时钟分配网络至关重要。设计师可以依赖其一致的性能来最小化时钟到达不同端点的时序差异。

三、 设计考量与应用领域

在采用NB3N2304NZDTG进行设计时,工程师需重点关注:

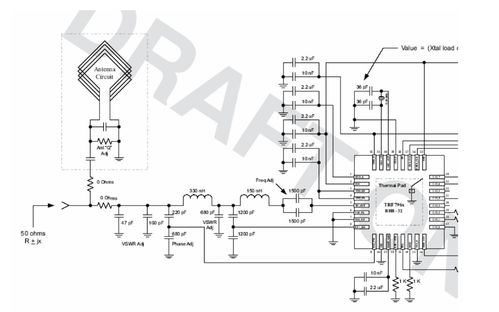

- 电源去耦:必须在电源引脚附近布置高质量的去耦电容(通常为0.1μF和0.01μF并联),以滤除噪声,保证电源完整性,这是实现低抖动性能的前提。

- PCB布局与阻抗匹配:输入和输出走线应作为受控阻抗传输线来处理,尤其是差分输入对,需保持等长、等距,并做好终端匹配,以最小化反射。

- 热管理:虽然功耗相对较低,但在高环境温度或全速运行下,仍需考虑其热耗散,确保结温在安全范围内。

其典型应用领域广泛,包括但不限于:

- 网络与通信设备:路由器、交换机、光纤通道卡中的时钟分配。

- 计算与存储:服务器主板、RAID控制器、高速背板。

- 工业与测试仪器:高性能示波器、信号发生器、自动化测试设备(ATE)。

- 消费电子:高端数字电视、机顶盒、A/V接收机中需要高质量时钟的部分。

结论

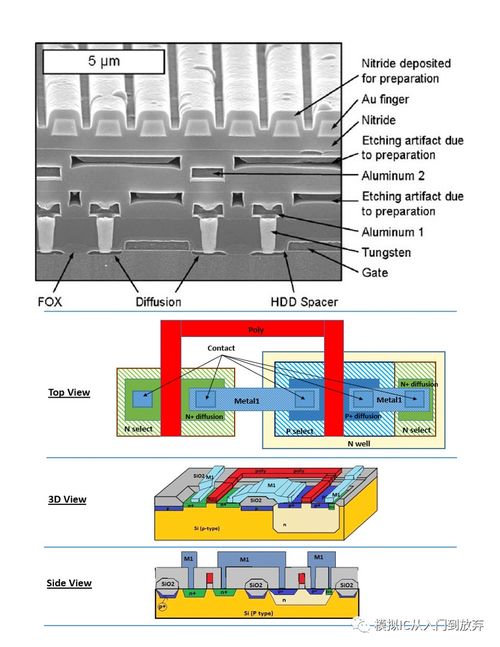

NB3N2304NZDTG时钟缓冲器驱动器代表了高性能时钟管理集成电路的一个成熟解决方案。它通过精心的内部电路设计——包括高性能的差分输入接收器、低噪声的放大驱动级以及稳定的偏置与电源管理电路——将时钟分配任务专业化、集成化。在追求更高数据速率和更严格时序余量的今天,此类器件的正确选型与应用,直接关系到整个数字系统能否稳定可靠地运行于性能巅峰,是集成电路与系统设计师手中不可或缺的关键棋子。

如若转载,请注明出处:http://www.58xiaolin.com/product/64.html

更新时间:2026-04-14 10:04:58