基于NFC的无线通信系统集成电路设计

近场通信(NFC)技术作为一种短距离、高频率的无线通信技术,已广泛应用于移动支付、身份识别、智能家居等领域。其核心在于高效、低功耗的集成电路设计,这直接决定了整个系统的性能、可靠性与成本。本文将探讨基于NFC的无线通信系统电路设计的核心模块与关键技术,特别是集成电路层面的实现方案。

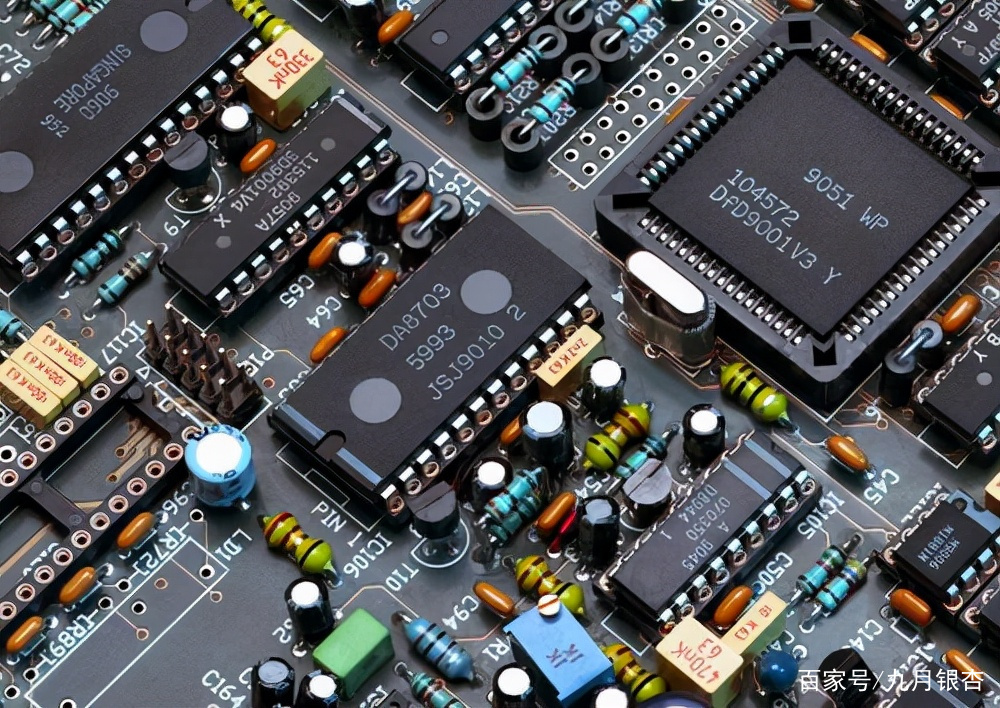

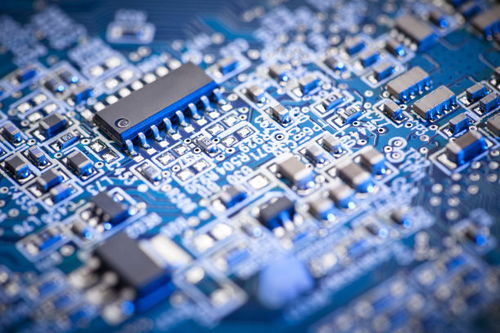

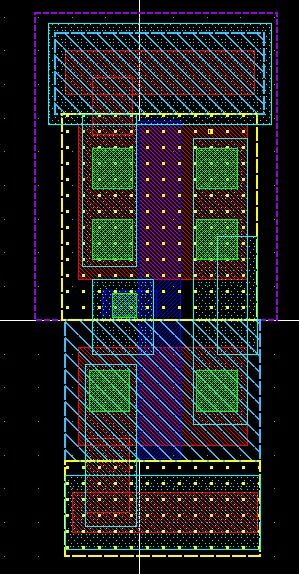

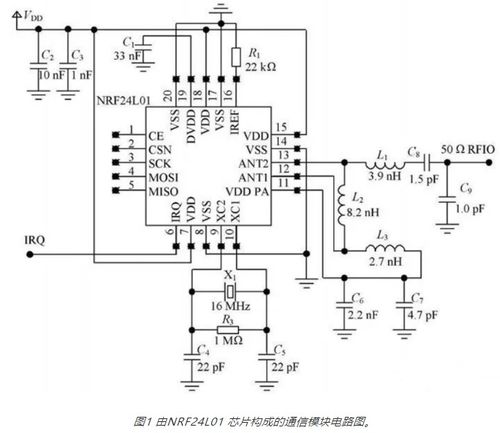

NFC系统的基本架构通常包括模拟前端(AFE)、数字基带处理器、存储器(如EEPROM)以及天线匹配网络。其集成电路设计需在单芯片上高度集成这些模块,并充分考虑与外部天线的接口。

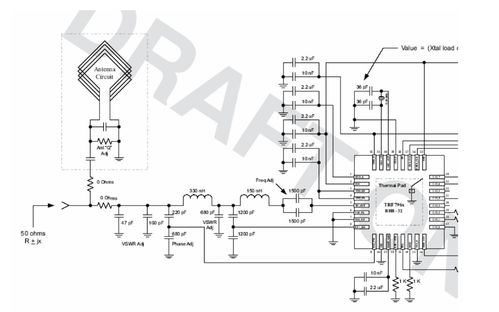

模拟前端电路是设计的重中之重。它主要包括射频接收路径、发射路径和电源管理单元。接收路径负责从天线拾取微弱的13.56MHz载波信号,经低噪声放大器(LNA)放大后,通过包络检波或相干解调等方式恢复出数字基带信号。发射路径则通过负载调制或主动发射模式,将数字基带信号调制到载波上,并通过功率放大器(PA)驱动天线。电源管理单元需高效地从射频场中获取能量(在无源模式下),为整个芯片供电,这需要精心设计整流器(通常采用倍压或多级结构)和稳压电路,以确保在变化的场强下提供稳定的工作电压。

数字基带处理器的设计关乎协议实现的效率与灵活性。它需要集成状态机、编解码器(如Miller、Manchester)、循环冗余校验(CRC)模块以及防冲突算法处理器。现代设计常采用可配置的处理器核(如ARM Cortex-M0)结合专用硬件加速器的方式,在保证处理速度的降低功耗并增强对多种NFC协议(如ISO/IEC 14443 Type A/B, FeliCa)的支持能力。

天线匹配网络虽常作为片外分立元件,但其设计与芯片的输入输出阻抗紧密相关。集成电路设计时必须优化发射驱动器的输出阻抗和接收器的输入阻抗,以最大程度地减少片外匹配元件的数量与复杂度,降低整体方案成本并提高能量传输效率。

在集成电路的物理实现层面,面临的主要挑战包括:

- 低功耗设计:尤其是对于无源标签芯片,所有电路必须在极低的功耗下工作。这需要采用特殊的低功耗逻辑、时钟门控、电源域隔离等技术。

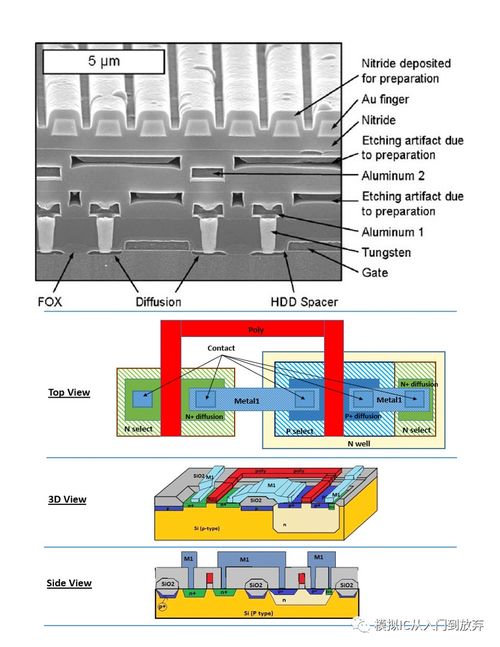

- 射频性能优化:在深亚微米CMOS工艺下,设计高线性度、高效率的功率放大器和高灵敏度的低噪声放大器,并处理好数字电路对敏感模拟电路的噪声耦合。

- 高集成度与成本控制:需要选择合适的工艺节点(如0.18μm或0.13μm CMOS),在芯片面积、性能和成本之间取得平衡。

- 安全性与可靠性:对于支付等应用,需集成硬件加密引擎、真随机数发生器(TRNG)和防侧信道攻击机制,同时确保芯片在ESD、RF场强突变等恶劣环境下稳定工作。

基于NFC的无线通信系统集成电路设计正朝着更高集成度(集成传感器、显示驱动等)、更低功耗(能量收集技术)、更强安全(集成安全元件SE)以及更广泛的应用场景(如物联网节点)发展。通过系统级架构优化、先进的混合信号设计方法和不断演进的半导体工艺,NFC芯片将继续为无缝、安全的无线连接提供核心动力。

如若转载,请注明出处:http://www.58xiaolin.com/product/70.html

更新时间:2026-04-14 16:03:07