集成电路版图设计 芯片设计的物理实现艺术

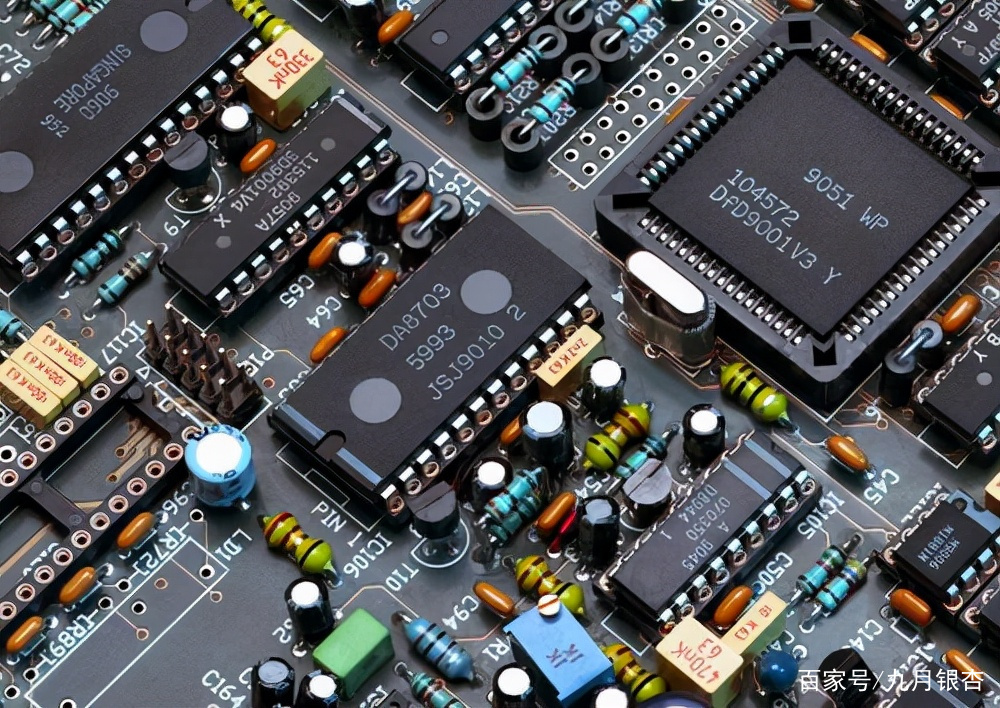

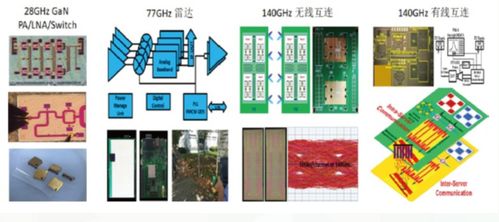

在当今信息时代的核心,集成电路(IC)构成了所有电子设备的大脑与心脏。从智能手机到超级计算机,从智能家居到航天器,其卓越性能的基石便是那精妙绝伦的集成电路设计。这一宏大工程通常被划分为前后端,而集成电路版图设计,正是连接抽象电路构想与实体硅芯片的桥梁,是芯片设计流程中至关重要的物理实现阶段。

一、 集成电路设计:从构想到蓝图

在深入版图设计之前,我们首先需要理解其上游环节——集成电路设计。这通常指逻辑设计或电路设计,属于设计流程的前端。

- 系统架构与功能定义:设计始于明确芯片的规格,如处理速度、功耗、面积、功能模块等。

- 寄存器传输级(RTL)设计:工程师使用硬件描述语言(如Verilog或VHDL),以代码的形式描述芯片各模块的逻辑功能和数据流。此时的设计还是与工艺无关的抽象行为描述。

- 逻辑综合:利用电子设计自动化(EDA)工具,将RTL代码映射到特定的工艺库(由芯片代工厂提供),生成门级的网表。这个网表是由标准逻辑门(如与门、或门、非门、触发器等)及其连接关系构成的电路图。

至此,一个“应该做什么”的功能性电路蓝图已经完成,但它尚未告诉我们如何在硅片上“物理地”构建它。这便是版图设计的使命。

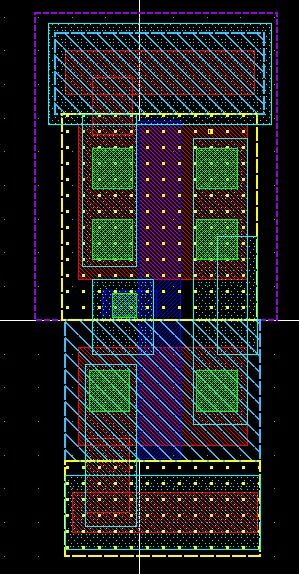

二、 集成电路版图设计:蓝图的物理雕刻

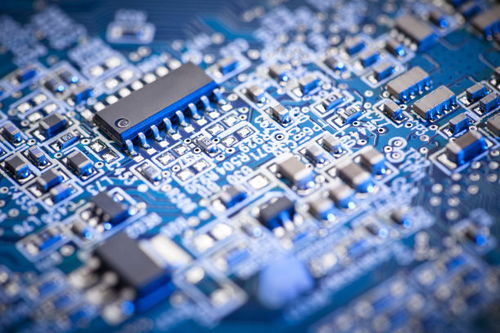

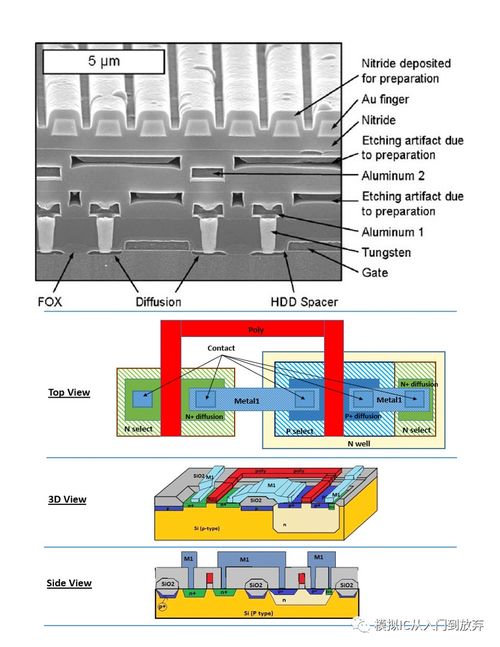

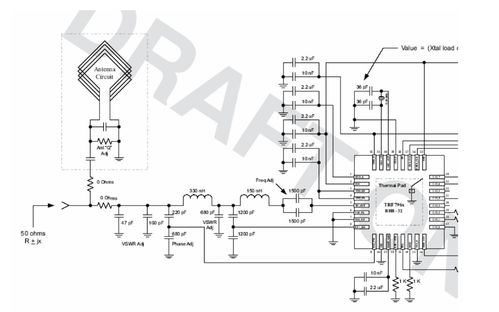

集成电路版图设计,又称物理设计,是将逻辑综合后的门级网表,转化为一系列可供芯片制造光刻使用的几何图形(版图)的过程。这些图形定义了硅片上每一层(如扩散层、多晶硅层、金属连接层等)的形状、尺寸和位置。

其核心流程与挑战包括:

- 布局规划:如同城市规划,需要确定芯片上各个大型功能模块(如CPU核心、内存控制器等)的摆放位置,规划电源网络和全局布线通道,以优化芯片面积、信号时序和功耗。

- 标准单元布局:将网表中的数百万甚至数十亿个标准逻辑单元(如反相器、触发器)合理地放置在芯片核心区域内,目标是减少总布线长度和信号延迟。

- 时钟树综合:构建一个低偏移、低功耗的全局时钟分布网络,确保芯片所有时序单元能在同一时刻精准同步,这是高性能设计的关键。

- 布线:这是最复杂的步骤之一,负责用金属线将所有单元按照网表连接起来。它必须遵守严格的设计规则,同时优化信号完整性、串扰和电迁移等问题。现代芯片拥有十多层金属互连,布线犹如在微观世界进行立体交通规划。

- 物理验证:版图完成后,必须经过严格的验证:

- 设计规则检查:确保版图符合芯片代工厂的制造工艺极限(如最小线宽、最小间距)。

- 版图与原理图比对:确保物理版图与原始逻辑网表在电气连接上完全一致,杜绝任何错接、漏接。

- 电气规则检查:检查天线效应、短路、开路等潜在电气问题。

- 后仿真与签核:从最终版图中提取出包含所有寄生电阻、电容的详细参数,进行精确的时序、功耗和信号完整性分析。只有所有指标均满足要求,设计才能“签核”并交付制造。

三、 设计与版图:相辅相成,密不可分

集成电路设计与版图设计并非割裂的环节,而是深度迭代、紧密协作的关系:

- 前端指导后端:逻辑设计定义了电路的功能和性能目标,为版图设计提供了根本依据。

- 后端反馈前端:在物理实现过程中发现的时序、功耗、面积等问题,会反馈给前端设计者,可能需要修改RTL代码或架构以进行优化。这种迭代是现代芯片设计,尤其是高性能芯片设计的常态。

- EDA工具的纽带:强大的EDA工具链贯穿始终,实现了从RTL到GDSII(最终版图数据格式)的自动化或半自动化流程,极大提升了设计效率和可靠性。

###

如果说集成电路设计是赋予芯片灵魂(功能)的乐章创作,那么集成电路版图设计就是指挥乐团,将每个音符(晶体管和连线)精确安排在乐谱(硅片)上,最终演奏出完美交响乐的物理实现艺术。随着工艺节点不断微缩至纳米乃至埃米尺度,版图设计面临的物理效应挑战日益严峻,其重要性愈发凸显。正是这两大领域的工程师们通力合作,在方寸之间进行着人类最精密的创造,持续推动着计算能力的边界,塑造着我们数字世界的未来。

如若转载,请注明出处:http://www.58xiaolin.com/product/72.html

更新时间:2026-04-14 12:07:19