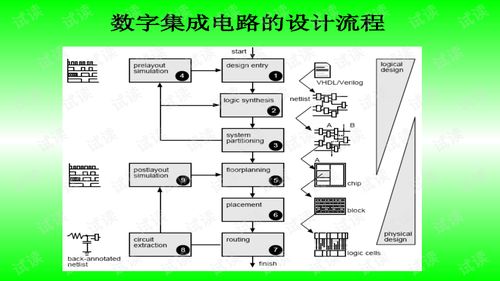

数字集成电路的设计流程 从概念到硅片

数字集成电路是现代电子系统的核心,其设计是一个复杂且高度规范化的工程过程,通常被称为“设计流程”。一个典型的数字IC设计流程,从抽象的系统构思开始,到最终物理硅片的生产与测试结束,涵盖了多个层次和阶段。它不仅是技术实现的过程,更是一个系统性的项目管理与优化过程。以下将详细介绍数字集成电路设计的主要流程。

1. 系统规格定义与架构设计

这是设计流程的起点。设计团队需要明确芯片的功能、性能指标(如速度、功耗、面积)、目标工艺节点、封装形式以及成本预算。在此基础上,进行系统级的架构设计,确定芯片的主要功能模块(如处理器核、存储器、接口控制器等)、模块间的互连方式(如总线、片上网络)以及整体的时钟和电源管理策略。这一阶段的输出是芯片的顶层架构文档和功能规格说明书。

2. 寄存器传输级设计

在架构确定后,设计进入寄存器传输级(RTL, Register-Transfer Level)设计阶段。这是数字逻辑设计的核心环节。设计工程师使用硬件描述语言(如Verilog或VHDL),以代码的形式精确描述芯片各模块在每一个时钟周期内的数据流动和逻辑操作。RTL代码描述的是可综合的逻辑功能,它定义了电路的功能行为,但独立于具体的物理实现。这一阶段需要严格的功能仿真,以确保逻辑行为符合规格定义。

3. 逻辑综合

RTL设计完成后,需要通过逻辑综合工具,将其转换为由标准单元库(如与门、或门、触发器等)和特定宏模块(如存储器、锁相环)组成的门级网表。综合过程需要在给定的工艺库、时序约束(如时钟频率)和面积/功耗约束下进行优化。综合后的网表是电路的逻辑连接关系图,它已经映射到了目标制造工艺。

4. 设计验证

验证贯穿于整个设计流程,但在网表生成后尤为重要。主要包括:

- 功能验证:通过仿真,确保门级网表的功能与RTL设计一致。

- 形式验证:使用数学方法,形式化地证明综合前后设计的功能等价性。

- 静态时序分析:在不进行仿真的前提下,通过分析所有可能的路径,来验证电路在所有工况下是否满足时序要求(建立时间、保持时间)。

- 功耗分析:评估电路的静态和动态功耗。

5. 物理设计

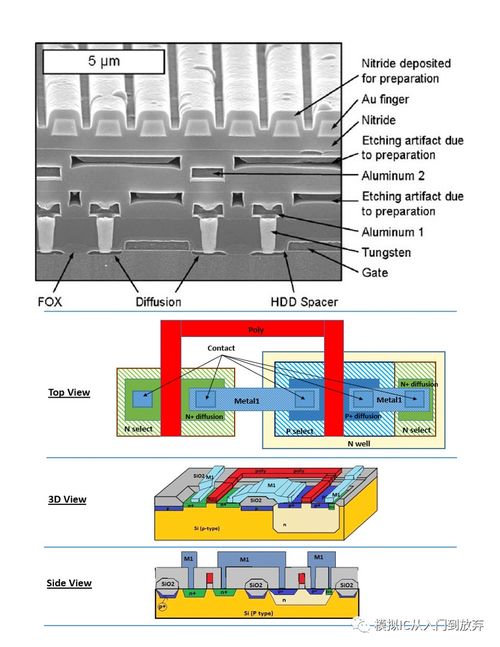

物理设计是将逻辑网表转化为实际物理版图(Layout)的过程,也称为“后端设计”。主要步骤包括:

- 布局规划:确定芯片核心区域、各个功能模块以及输入/输出单元的粗略位置。

- 单元布局:将标准单元精确地放置到芯片布局上。

- 时钟树综合:构建一个低偏斜、低功耗的全局时钟分布网络,确保时钟信号能同时到达所有时序单元。

- 布线:根据网表的连接关系,在单元之间进行金属连线。布线必须遵守制造工艺的设计规则。

- 寄生参数提取:从完成的版图中提取导线带来的电阻、电容等寄生效应参数。

- 版图后验证:将提取的寄生参数反标回网表,再次进行静态时序分析和功能仿真(后仿),确保物理实现后的电路依然满足所有性能与功能要求。还需要进行物理验证,包括设计规则检查(DRC)和版图与电路图一致性检查(LVS)。

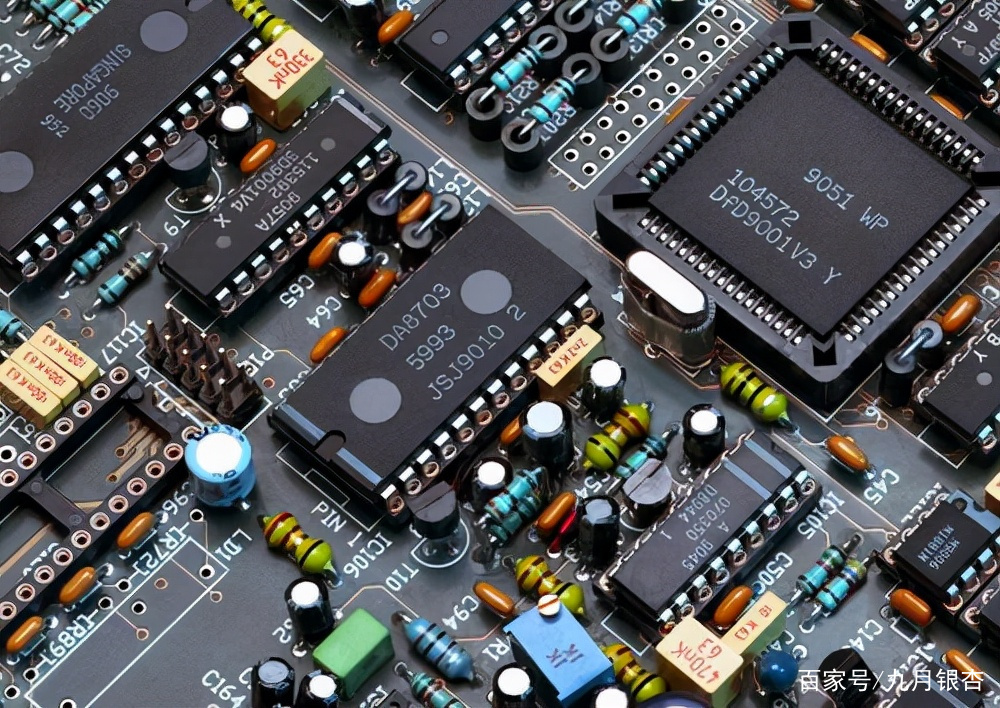

6. 流片与生产

当版图通过所有验证后,便可以生成最终交付给芯片制造厂(Foundry)的数据——GDSII格式的版图文件。这个过程称为“流片”(Tape-out)。晶圆厂使用此文件制作光掩模,并通过一系列复杂的光刻、刻蚀、掺杂等半导体工艺步骤,在硅晶圆上制造出实际的电路。

7. 封装、测试与量产

制造完成的晶圆经过切割、封装(将芯片核心封装到保护外壳并引出引脚),成为独立的集成电路芯片。随后进行严格的量产测试,包括功能测试、性能测试和可靠性测试,筛选出合格的产品。只有通过所有测试的芯片,才能最终交付给客户,应用于各类电子设备中。

###

数字集成电路的设计流程是一个迭代、求精的“自顶向下”与“自底向上”相结合的过程。每一阶段都伴随着严格的验证,以确保设计的正确性。随着工艺节点的不断进步和系统复杂度的指数级增长,设计流程也日益依赖于高度自动化的电子设计自动化(EDA)工具和严谨的设计方法论。理解并遵循这一完整流程,是成功设计出高性能、高可靠性芯片的基石。

如若转载,请注明出处:http://www.58xiaolin.com/product/81.html

更新时间:2026-04-18 19:17:00